자일링스의 기술과 하이레벨 합성의 제품 포트폴리오로 확장하게 되면, 시스템 디자이너와 하드웨어 디자이너들이 C, C++ 및 시스템 C의 하이레벨 언어 디자인에 익숙한 다양한 기업에게 프로그래머블 플랫폼의 장점을 제공할 수 있게 될 것이다. 또한 자일링스는 지금의 FPGA(field-programmable gate array)를 타깃으로 하는 복잡한 디자인을 위한 ESL(electronic system-level) 디자인 방법론을 지원하는 툴에 대한 증가하는 고객들의 요구에 부응할 수 있게 될 것이다.

AutoESL의 주력 제품인 AutoPilot은 하이레벨 합성 툴로써 생산성을 강화하고 비디오, 무선 및 고성능 컴퓨팅 애플리케이션의 출시 기간 단축을 위해 선도적인 반도체 및 시스템 업체들에 의해 채택되었으며, 그 중에서 25개 이상의 기업이 자일링스 고객이자 얼라이언스 프로그램의 회원사이다. 이번 인수를 통해, 자일링스는 6시리즈 및 7시리즈 FPGA와 새로운 확장형 프로세싱 플랫폼으로 디자이너 생산성 및 혁신을 제고할 예정이다.

월드와이드 마케팅 선임 부사장인 빈 랫포드(Vin Ratford)씨는 “자일링스는 수 년 동안 하이레벨 합성 기술을 구체화하여 왔다.”며 “2006년, 자사는 업계가 결과의 품질을 향상시키고 디자인 플로우 간소화하여 상호호환성을 확립하며, 임베디드 프로세싱 흐름을 개선하는 것을 지원하기 위해 ESL 이니셔티브에 착수했다”고 말했다.

“최근 하이레벨 합성 툴 제품을 평가하기 위해 독자적인 연구를 의뢰했다. BDTI와 자일링스 연구소가 실시한 벤치마크에 의하면, AutoPilot의 결과물의 품질이 데이터 경로가 많은 디자인과 DSP 디자인에 대해서 직접 RTL로 코딩된 결과물과 대등하거나 보다 우수한 것으로 드러났다. 자사는 AutoESL 팀이 자일링스의 일원이 된 것이 진심으로 기쁘며, 함께 FPGA 기반 ESL 디자인의 약속을 지킬 수 있을 것으로 믿어 의심치 않는다.”고 말했다.

자일링스는 인수 조건에 대해서는 공개하지 않았다. 현재 캘리포니아주 쿠퍼티노(Cupertino)의 본사와 중국 북경에서 근무중인 대부분의 AutoESL 직원들은 자일링스의 직원이 될 것이다.

BDTI(Berkeley Design Technology, Inc.)의 설립자이자 사장인 제프 비어(Jeff Bier)씨는 “역사적으로, FPGA 상에 직접 작성한 RTL 코드로 구현된 까다로운 애플리케이션들은 일반적으로 비교적 양질의 결과를 거두었지만 생산성이 좋지 않았으며, 반면에 DSP 프로세서 상에 구현된 애플리케이션들은 생산성은 뛰어났지만 결과적인 품질은 비교적 좋지 않았다”고 말했다. (출처: 2010년 2분기, Xcell 저널 지)

“FPGA와 프로그래머블 DSP 프로세서 사용의 균형을 취하는 다수 시스템 디자이너에게는 개발 시간이 주된 장애물이었다. 평가에 따르면 하이레벨 합성을 이용하는 이 새로운 접근방식은 BDTI 광학 플로우 워크로드와 같은 애플리케이션에 있어 이 장애물을 대부분 제거하는 것으로 보인다.”고 말했다.

BDTI는 FPGA에 하이레벨 합성 툴을 사용하게 될 사용자들이 이러한 툴의 기능과 한계를 즉시 파악할 수 있는 객관적이고 신뢰성 있는 데이터 및 분석을 제공하는 BDTI 하이레벨 합성 툴 인증 프로그램을 개발했다.

뉴스타운

뉴스타운TV 구독 및 시청료 후원하기

뉴스타운TV

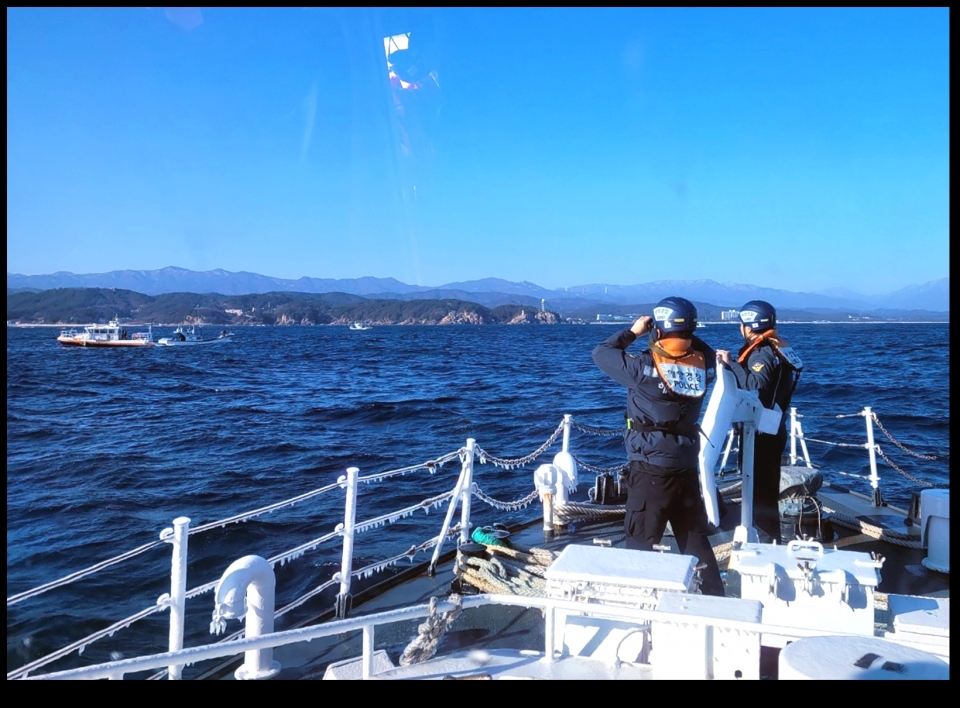

![[단독] 북한산 인수봉, 구조 헬기 긴급 출동 장면 포착!](/news/photo/202511/669971_628773_447.jpg)