과학기술부 21세기 프론티어 연구개발사업의 일환으로 발족한 테라급 나노소자 개발사업단(단장 : 이조원(李兆遠)박사)의 과제를 수행중인 한양대학교 전형탁(全鎣卓) 교수 연구팀은 한국표준과학연구원 조만호 박사팀과 공동으로 차세대 나노 CMOS 소자에 적용할 수 있는 '원거리 플라즈마 원자층 증착 기술' 개발에 성공했다고 밝혔다.

반도체 분야의 기술발전 예측에 의하면 2010년경 반도체 게이트 산화막의 두께는 핸드폰에 쓰이는 저 전력 소자의 경우 0.8~1.2 nm, 컴퓨터 CPU와 같은 고성능 소자에서는 0.5~0.8 nm에 이를 것으로 예상되고 있다.

그러나 현재 게이트 산화막으로 사용되는 SiO2(이산화실리콘)으로는 얇아진 박막 두께로 인해 전류의 누설이 일어나 반도체 소비전력이 급격하게 증가하게 되기 때문에 SiO2보다 유전상수가 큰 고유전체 산화막으로 교체하려는 연구가 진행되고 있다.

이러한 고유전체 산화막을 나노크기에서 박막화하는데 필수적으로 사용되는 기술이 원자층 증착기술(ALD : Atomic Layer Deposition)이다.

기존의 ALD 공정으로 여러 소재를 이용하여 우수한 특성을 가지는 박막을 형성하려고 하였으나 박막증착시 이온들에 의해 기판 및 박막에 손상을 가져와 박막의 특성이 나빠지는 결과를 가져왔다.

특히 전하의 이동성 저하로 인해 Intel을 비롯한 반도체 업체들은 2008년도 이전에 45nm급 CMOS소자에 고유전체 게이트 산화막을 적용하려던 계획을 2010년 이후 32nm 이하기술로 미루게 되었다.

이러한 상황에서 전교수 연구팀이 개발한 “원거리 플라즈마 ALD" 기술과 이를 이용한 원자층 증착 장치는 플라즈마 발생지역과 기판사이의 간격을 기존의 방식보다 크게 하여 플라즈마 이온에 의한 영향을 최소화함으로써 기판과 박막의 손상을 획기적으로 줄였다.

또한 이 장치로 실험한 결과 직접(direct) 플라즈마 방식에 비해 전자이동도가 50% 향상되어 앞으로 이 기술이 테라급 나노 CMOS소자를 제작하는데 필수적인 기술이 될 것으로 기대된다.

이번 연구성과는 Applied Physics Letters(APL) 8월호에 게재되었으며 미국 진공학회가 주최하는 ALD 2005학회에서 발표할 계획이다.

그 밖에 관련 논문을 APL, JAP, ECS, JVST등의 SCI journal에 30편 이상 게재하였으며 이 기술과 관련하여 국제특허 1건과 국내 특허 6건을 출원 중이다.

VLSI research에 의하면 전세계 ALD 시장은 2005년 7억 3천만달러로 매년 100% 이상의 성장률을 보여 왔고 2006년경에는 15억달러 정도로 성장할 것이며 2010년에는 50억 달러 이상의 시장이 될 것으로 전망되고 있다.

따라서 ALD 시장에서 전교수 연구팀이 개발한 원거리 플라즈마 증착 기술이 주요 기술이 될 것이며 우리나라가 앞으로도 지속적으로 ALD 분야에서 세계를 주도해 나가는 계기가 될 것으로 기대된다.

뉴스타운

뉴스타운TV 구독 및 시청료 후원하기

뉴스타운TV

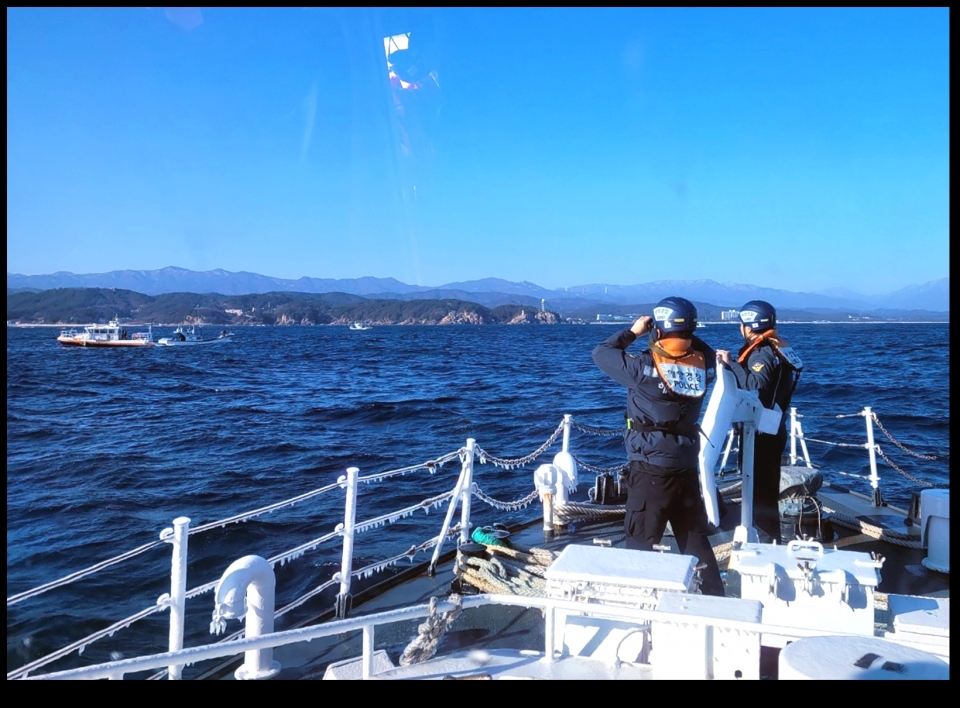

![[단독] 북한산 인수봉, 구조 헬기 긴급 출동 장면 포착!](/news/photo/202511/669971_628773_447.jpg)