퀄리타스반도체가 PCIe(Peripheral Component Interconnect Express) 6.0 PHY IP 솔루션을 발표했다. 이 솔루션은 5nm공정에서 개발되었으며 AI시대의 방대한 데이터 전송에 필요한 대역폭과 속도를 충족한다.

PCIe는 High-speed serial computer bus의 표준으로 가장 고속인 범용 인터페이스로 자리잡고 있다. 2003년 PCIe 1.0 버전이 출시된 이후, 각 세대마다 두배의 속도 향상을 이루어 왔다. 2023년 초 인텔이 출시한 사파이어 래피즈 CPU에는 PCIe 5.0이 적용되어 현재의 메인스트림으로 자리잡았으며 퀄리타스반도체는 PCIe 6.0 개발을 통해 선도적인 기술 로드맵을 구축하고 있다.

퀄리타스반도체의 PCIe 6.0 PHY IP는 레인당 최대 64GT/s의 전송 속도를 자랑하며, 최대 16개의 레인을 사용하여 양방향 통신 시 초당 최대 256GB/s의 데이터 전송이 가능하다. 퀄리타스반도체는 PCIe 6.0 PHY IP 테스트칩을 통해 64GT/s 속도의 데이터 송신과 수신이 이루어지는것을 검증하였다. 이를 위해 퀄리타스반도체는 100G 전송 속도의 PAM4(멀티레벨 시그널링 서데스) 기술을 확보하였고, 아날로그방식과 더불어 디지털 방식의 DSP(Digital Signal Processing)기술도 개발하여 정확성을 높였다. 이로써 퀄리타스반도체는 글로벌 정상급의 기술 경쟁력을 갖추게 된 것이다. 앞으로 퀄리타스반도체는 컨트롤러 IP와의 호환성 검증을 위해 2차 테스트칩을 제작할 예정이다.

딥러닝의 등장으로 인공지능 기술의 발전과 수요가 급증함에 따라, 높은 정확성과 대량의 데이터 처리능력이 요구되고 있다. 컴퓨트익스프레스링크(CXL)는 기존 메모리 시스템을 대체할 기술로 주목받고 있으며 PCIe PHY IP 기술이 CPU와 그래픽처리장치(GPU)등 여러장치와 메모리를 연결하는 CXL 인터페이스 기술에 활용되고 있다. 퀄리타스반도체의 PCIe PHY IP는 PCIe 표준을 준수하여 CXL의 물리계층으로 활용 될 수 있어, 차세대 메모리시장에서 중요한 역할을 할 것으로 기대된다.

퀄리타스반도체는 2021년 PCIe 4.0 PHY IP 솔루션을 8nm 공정에서 첫 라이센싱하였으며, 올해 중국 고객사와 라이센싱 계약을 통해 기술의 신뢰성과 성능을 인정 받았다. 이번 PCIe 6.0 PHY IP 또한 여러 고객사들에게 프로모션을 시작하였으며 대다수의 고객사들에게서 구체적인 문의가 있어 시장에서 독보적인 입지를 굳힐 것으로 보인다. 퀄리타스반도체는 이번에 개발 된 5nm 공정 뿐만아니라 4nm와 2nm에서도 PCIe 6.0 PHY IP를 개발할 예정이다. 퀄리타스반도체의 김두호 대표는 “이번 PCIe 솔루션 개발로 인공지능 기술을 엣지 환경에서 구현할 중요한 반도체 설계 IP 포트폴리오를 확보했으며, 고부가가치 IP인 PCIe PHY를 국내 최초로 자체 개발한 것에 대해 모든 임직원이 뿌듯하게 생각한다”고 말했다. 또한 “앞으로 퀄리타스반도체가 반도체 IP 시장에서 기록할 마일스톤에 기대해 달라”고 전했다.

뉴스타운

뉴스타운TV 구독 및 시청료 후원하기

뉴스타운TV

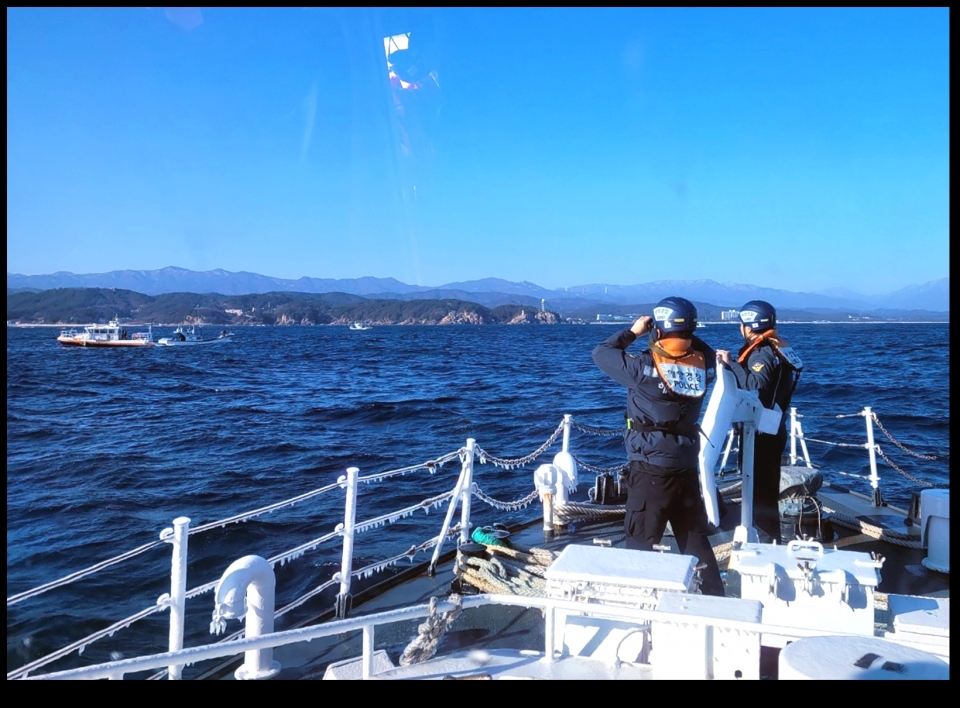

![[단독] 북한산 인수봉, 구조 헬기 긴급 출동 장면 포착!](/news/photo/202511/669971_628773_447.jpg)